### 5 MHz-9000 MHz

### **Product Description**

The BSW6620 is an absorptive SPDT  $50\Omega$  matched RF switch supporting bandwidth up to 9GHz. It's high linearity performance across the temperature range makes it ideally suitable for use in 3G/4G/5G/6G wireless infrastructure and 802.11 a/n/ac/ax applications where high isolation and excellent performance is required.

The BSW6620 is designed with robust ESD protection circuits at all pins and packaged in an industry standard, fully RoHS2-compliant, 16Lead, 4mm x 4mm x 0.9mm QFN package.

The BSW6620 does not require blocking capacitors. If DC is presented at the RF port, add a blocking capacitor.

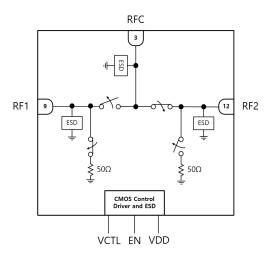

A functional block diagram is shown in Figure 1.

#### **Block Diagram**

Figure 1. Functional Block Diagram

#### **Applications**

- Wireless 3G/4G/5G/6G Infrastructure

- Base station & Repeater

- WLAN 802.11 a/b/ac/ax

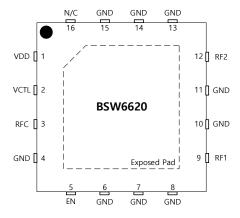

### **Package Type**

4mm x 4mm x 0.9mm, 16-Lead QFN Package

Figure 2. Package type

#### **Device Features**

• Supply Voltage: 2.7V to 5.5V

• Low Insertion Loss

: 0.72dB @ 2GHz

: 0.83dB @ 4GHz

: 0.74dB @ 6GHz

: 1.02dB @ 7.2GHz

Ultra High Isolation

- RFC to RFx

: 65dB @ 2GHz

: 58dB @ 4GHz

: 54dB @ 6GHz

: 49dB @ 7.2GHz

- RFx to RFx

: 56dB @ 2GHz

: 50dB @ 4GHz

: 46dB @ 6GHz

: 42dB @ 7.2GHz

• Switching time: 120 to 240ns

• ESD, HBM: ±2.0kV @All pins

• Operating temperature range : -40°C to +105°C

### 5 MHz-9000 MHz

### **Electrical Specifications**

Typical conditions are at VDD = 5V,  $T_A$  = +25°C, VCTL/EN Low = 0V, VCTL/EN High = 3.3V,  $Z_L$  = 50 $\Omega$ , excluding SMA Connector and PCB losses<sup>(1)</sup>, unless otherwise noted.

**Table 1. Electrical Specifications**

| Parameter                        | Path            | Condition                                                                                 | Min | Тур                                                                  | Max  | Unit |

|----------------------------------|-----------------|-------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------|------|------|

| Operating Frequency              |                 |                                                                                           | 5   |                                                                      | 9000 | MHz  |

| Insertion Loss                   | RFC - RFx       | 1GHz<br>2GHz<br>3GHz<br>4GHz<br>5GHz<br>6GHz<br>7GHz<br>8GHz<br>9GHz                      |     | 0.61<br>0.72<br>0.96<br>0.83<br>0.79<br>0.74<br>0.88<br>1.04<br>1.80 |      | dB   |

| Isolation<br>(C to X)            | RFC - RFx       | 1GHz<br>2GHz<br>3GHz<br>4GHz<br>5GHz<br>6GHz<br>7GHz<br>8GHz<br>9GHz                      |     | 75<br>70<br>61<br>56<br>54<br>53<br>50<br>45                         |      | dB   |

| Isolation<br>(X to X)            | RFx - RFx       | 1GHz<br>2GHz<br>3GHz<br>4GHz<br>5GHz<br>6GHz<br>7GHz<br>8GHz<br>9GHz                      |     | 61<br>55<br>52<br>49<br>46<br>44<br>42<br>40<br>39                   |      | dB   |

| Return Loss<br>(Active Port)     | RFC / RF1 / RF2 | 5MHz—2GHz<br>2GHz—5GHz<br>5GHz—8GHz<br>8GHz—9GHz                                          |     | 23/21/21<br>15/15/15<br>20/20/15<br>10/10/10                         |      | dB   |

| Return Loss<br>(Terminated Port) | RFC / RF1 / RF2 | 5MHz—2GHz<br>2GHz—5GHz<br>5GHz—8GHz<br>8GHz—9GHz                                          |     | 25/17/17<br>15/15/15<br>20/15/15<br>10/12/12                         |      | dB   |

| Switching time                   | RFC - RFx       | 50% CTRL to 90% RF<br>50% CTRL to 10% RF                                                  |     | 240<br>120                                                           |      | ns   |

| Settling time                    | RFC - RFx       | 50% CTRL to 0.05dB final value Rising Edge<br>50% CTRL to 0.05dB final value Falling Edge |     | 320<br>150                                                           |      | ns   |

(1)Excluding SMA Connector and PCB loss.

1GHz (0.24dB), 2GHz (0.34dB), 3GHz (0.37dB), 4GHz (0.49dB), 5GHz (0.49dB), 6GHz (0.68dB), 7GHz (0.78dB), 8GHz (0.73dB), 9GHz (0.82dB)

### 5 MHz-9000 MHz

### **Electrical Specifications**

Typical conditions are at VDD = 5V,  $T_A$  = +25°C, VCTL/EN Low = 0V, VCTL/EN High = 3.3V,  $Z_L$  = 50 $\Omega$ , excluding SMA Connector and PCB losses<sup>(1)</sup>, unless otherwise noted.

**Table 1. Electrical Specifications (Cont.)**

| Parameter                    | Path      | Condition                   | Min | Тур                  | Max  | Unit     |

|------------------------------|-----------|-----------------------------|-----|----------------------|------|----------|

| Operating Frequency          |           |                             | 5   |                      | 9000 | MHz      |

| Input P1dB                   | RFC - RFx | 2.35GHz<br>3.5GHz<br>4.9GHz |     | 36.5<br>35.7<br>35.8 |      | dBm      |

| Input IP2 <sup>(2)</sup>     | RFC - RFx | 2.35GHz<br>3.5GHz<br>4.9GHz |     | 112<br>107<br>102    |      | dBm      |

| Input IP3 <sup>(2)</sup>     | RFC - RFx | 2.35GHz<br>3.5GHz<br>4.9GHz |     | 66<br>68<br>65       |      | dBm      |

| 2nd Harmonics <sup>(3)</sup> | RFC - RFx | 2.35GHz<br>3.5GHz<br>4.9GHz |     | 100<br>95<br>92      |      | dBc      |

| 3rd Harmonics <sup>(3)</sup> | RFC - RFx | 2.35GHz<br>3.5GHz<br>4.9GHz |     | 101<br>105<br>96     |      | dBc      |

| Maximum<br>Spurious Level    | RFC - RFx | 5MHz—9GHz <sup>(4)</sup>    |     | <-145                |      | dBm/10Hz |

<sup>(2)</sup> The each-tone Power is 20dBm and Tone spacing is 1MHz.

<sup>(3)</sup>Tone Power is 20dBm.

<sup>(4)</sup>No spurious signals were detected in all Frequency range.

### 5 MHz-9000 MHz

### **Product Description**

Figure 3. Pin Description (Top View)

**Table 2. Pin Descriptions**

| Pin No.                           | Pin Name    | Description                                     |

|-----------------------------------|-------------|-------------------------------------------------|

| 1                                 | VDD         | Supply Voltage.                                 |

| 2                                 | VCTL        | Switch Control Input.<br>(Referring to Table 3) |

| 3                                 | RFC         | RFC Port.                                       |

| 4, 6, 7, 8, 10,<br>11, 13, 14, 15 | GND         | Ground.                                         |

| 5                                 | EN          | Switch Control Input.                           |

| 3                                 | EIN         | (Definition for the EN pin, See Table 3)        |

| 9                                 | RF1         | RF1 Port.                                       |

| 12                                | RF2         | RF2 Port.                                       |

|                                   |             | Internal connection to Ground, External         |

| 16                                | N/C         | connection to PCB Ground Recommended            |

|                                   |             | to maximize isolation.                          |

| Pad                               | Exposed Pad | Ground.                                         |

**Table 3. Control Truth Table**

| VCTL | EN | RFC-RF1 | RFC-RF2 |

|------|----|---------|---------|

| 1    | 0  | ON      | OFF     |

| 0    | 0  | OFF     | ON      |

| 0    | 1  | OFF     | OFF     |

| 1    | 1  | OFF     | OFF     |

**Table 4. Operating Ranges**

| Parameter                         | Symbol            | Min | Typical | Max  | Unit |

|-----------------------------------|-------------------|-----|---------|------|------|

| Supply Voltage                    | VDD               | 2.7 |         | 5.5  | V    |

| Supply Current                    | IDD               | -   | 210     | -    | μА   |

| Digital Input Control (VCTI /FNI) | $VL_{High}$       | 1.0 | -       | 3.3  | V    |

| Digital Input Control (VCTL/EN)   | $VL_{Low}$        | 0   | -       | 0.7  | V    |

| Operating Temperature Range       | To                | -40 | +25     | +105 | °C   |

| RF Input Power, CW                | P <sub>CWOP</sub> | -   | -       | 33   | dBm  |

### 5 MHz-9000 MHz

**Table 5. Absolute Maximum Ratings**

| Parameter                       |           |                     | Symbol              | Min        | Max   | Unit |

|---------------------------------|-----------|---------------------|---------------------|------------|-------|------|

|                                 | Supply Vo | oltage              | VDD                 | -0.3       | 5.5   | V    |

| Digital Input Voltage           |           | VCTL / EN           | -0.3                | 3.6        | V     |      |

| Maximum Input Power, CW (+25°C) |           | RF <sub>CWMAX</sub> | -                   | Input P1dB | dBm   |      |

| Storage Temperature Range       |           | T <sub>ST</sub>     | -65                 | +150       | °C    |      |

| ESD                             | НВМ       | ALL pins            | V <sub>ESDHBM</sub> |            | ±2000 | V    |

| ESD                             | CDM       | ALL pins            | V <sub>ESDCDM</sub> |            | ±1000 | V    |

### **Table 6. Package Thermal Characteristics**

| Parameter                              | Symbol        | Value | Unit |

|----------------------------------------|---------------|-------|------|

| Junction to Ambient Thermal Resistance | $\theta_{JA}$ | 43.2  | °C/W |

5 MHz-9000 MHz

# **Ultra High Isolation SPDT RF Switch**

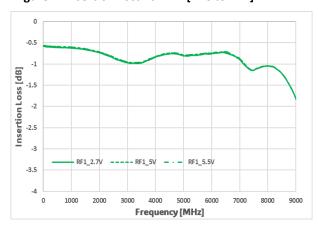

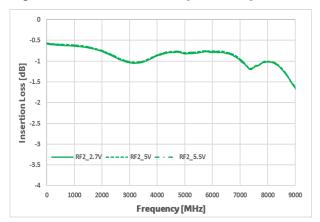

#### **Typical Performances**

Typical conditions are at VDD = 5V, T<sub>A</sub> = 25°C, VCTL/EN Low = 0V, VCTL/EN High = 3.3V, Z<sub>L</sub> = 50Ω, Excluding SMA Connector and PCB losses, unless otherwise noted.

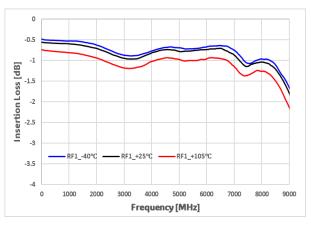

Figure 4. Insertion Loss vs VDD [RFC to RF1]

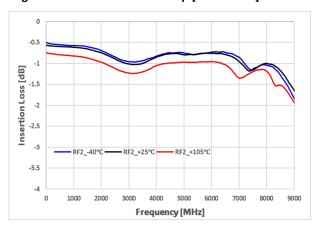

Figure 5. Insertion Loss vs VDD [RFC to RF2]

Figure 6. Insertion Loss vs Temp [RFC to RF1]

Figure 7. Insertion Loss vs Temp [RFC to RF2]

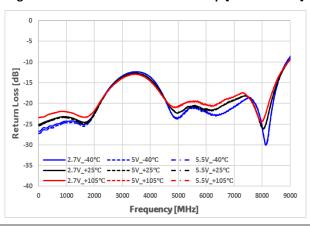

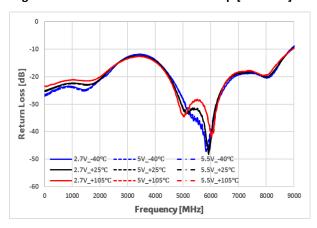

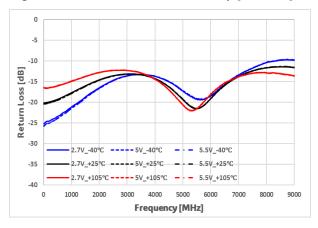

Figure 8. RFC Port Return Loss vs Temp [RF1 On state]

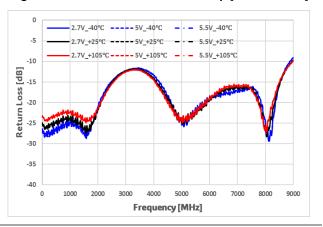

Figure 9. RFC Port Return Loss vs Temp [RF2 On state]

**BeRex**

•website: www.berex.com

•email: sales@berex.com

### **Typical Performances**

Typical conditions are at VDD = 5V,  $T_A$  = 25°C, VCTL/EN Low = 0V, VCTL/EN High = 3.3V,  $Z_L$  = 50 $\Omega$ , Excluding SMA Connector and PCB losses, unless otherwise noted.

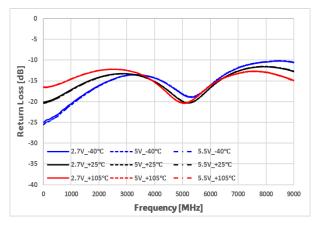

Figure 10. RF1 Port Return Loss vs Temp [On state]

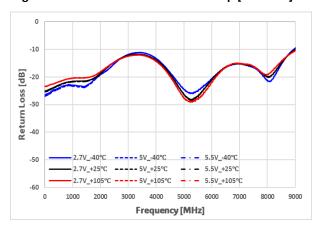

Figure 12. RF1 Port Return Loss vs Temp [Off state]

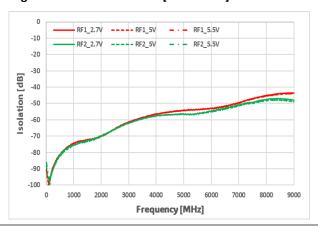

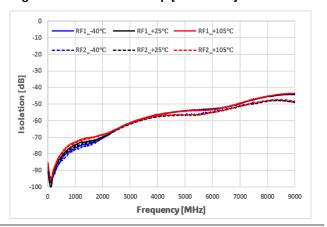

Figure 14. Isolation vs VDD [RFC to RFx]

Figure 11. RF2 Port Return Loss vs Temp [On state]

Figure 13. RF2 Port Return Loss vs Temp [Off state]

Figure 15. Isolation vs Temp [RFC to RFx]

**BeRex** •website: www.berex.com •email:

•email: sales@berex.com

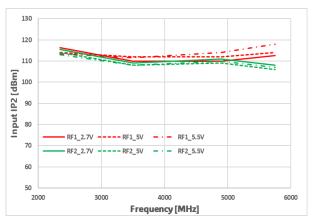

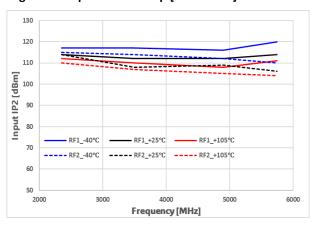

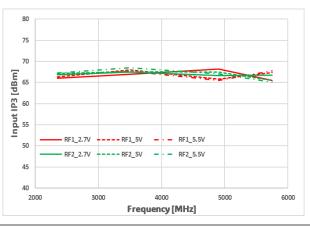

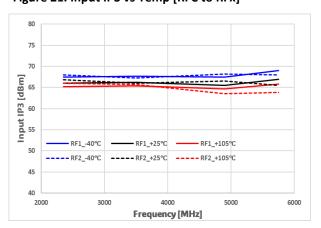

#### **Typical Performances**

Typical conditions are at VDD = 5V,  $T_A$  = 25°C, VCTL/EN Low = 0V, VCTL/EN High = 3.3V,  $Z_L$  = 50 $\Omega$ , Excluding SMA Connector and PCB losses, unless otherwise noted.

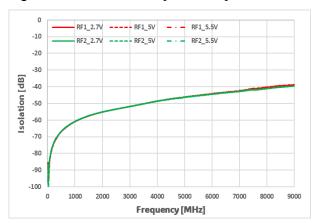

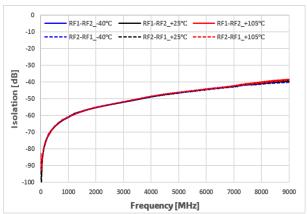

Figure 16. Isolation vs VDD [RFx to RFx]

Figure 17. Isolation vs Temp [RFx to RFx]

Figure 18. Input IP2 vs VDD [RFC to RFx]

Figure 19. Input IP2 vs Temp [RFC to RFx]

Figure 20. Input IP3 vs VDD [RFC to RFx]

Figure 21. Input IP3 vs Temp [RFC to RFx]

**BeRex**

•website: www.berex.com

•email: sales@berex.com

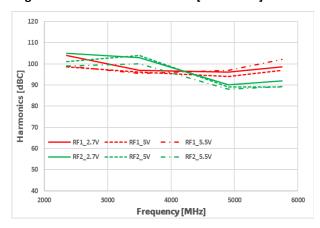

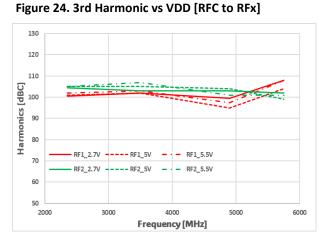

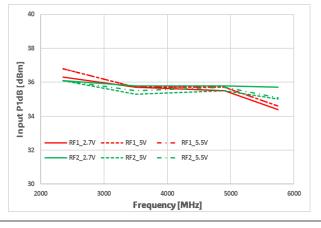

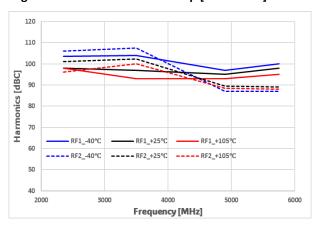

### **Typical Performances**

Typical conditions are at VDD = 5V,  $T_A$  = 25°C, VCTL/EN Low = 0V, VCTL/EN High = 3.3V,  $Z_L$  = 50 $\Omega$ , Excluding SMA Connector and PCB losses, unless otherwise noted.

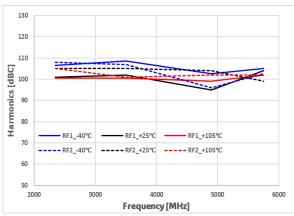

Figure 22. 2nd Harmonic vs VDD [RFC to RFx]

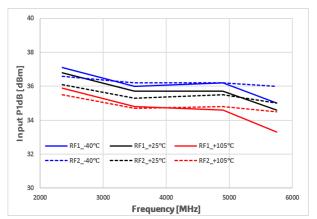

Figure 26. Input P1dB vs VDD [RFC to RFx]

Figure 23. 2nd Harmonic vs Temp [RFC to RFx]

Figure 25. 3rd Harmonic vs Temp [RFC to RFx]

Figure 27. Input P1dB vs Temp [RFC to RFx]

•email: sales@berex.com

•website: www.berex.com

**BeRex**

9

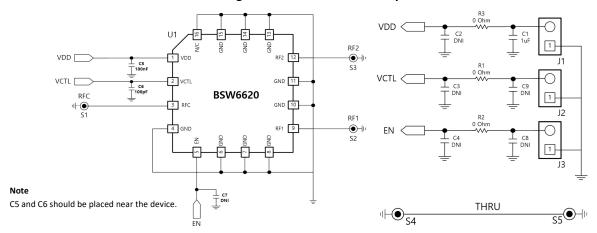

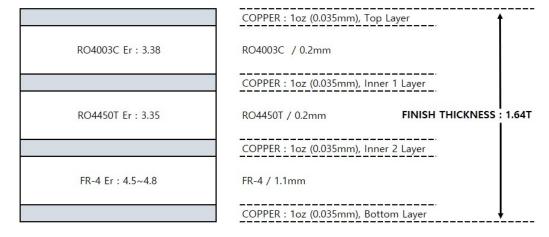

#### **Evaluation Board**

Figure 28. Evaluation Board Layout

Figure 29. Evaluation Board Schematic

**Table 7. Bill of Material - Evaluation Board**

| No. | Ref Des             | Part Qty | Part Number          | Remark |

|-----|---------------------|----------|----------------------|--------|

| 1   | C1                  | 1        | CAP 1005 1uF J 50V   |        |

| 2   | C5                  | 1        | CAP 1005 100nF J 50V |        |

| 3   | C6                  | 1        | CAP 1005 100pF J 50V |        |

| 4   | C2,C3,C4,C7,C8,C9   | 6        | CAP 1005 DNI         |        |

| 5   | R1,R2,R3            | 3        | RES 1005 0 ohm       |        |

| 6   | J1,J2,J3            | 3        | 2 Pin Header 2.54mm  |        |

| 7   | \$1,\$2,\$3,\$4,\$5 | 5        | SMA_END_LAUNCH       |        |

| 8   | U1                  | 1        | BSW6620              |        |

BeRex ●website: <u>www.berex.com</u> ●email: <u>sales@berex.com</u> 10

#### **Evaluation Board**

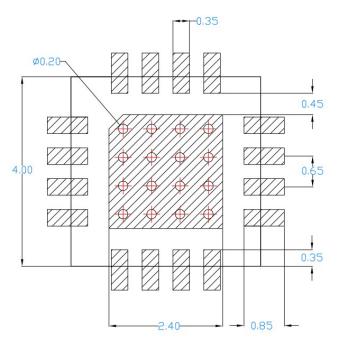

Figure 30. Suggested PCB Land Pattern

Figure 31. Evaluation Board PCB Layer Information

### 5 MHz-9000 MHz

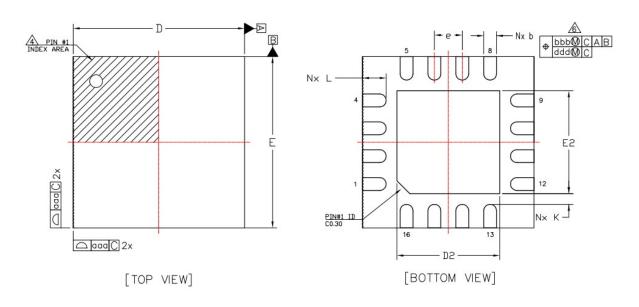

### **Package Outline Drawing**

#### NOTES:

- 1. Dimensioning and tolerancing conform to ASME Y14.5-2009.

- 2. All dimensions are in millimeters.

- 3. N is the total number of terminals.

- The location of the marked terminal #1 identifier is within the hatched area.

- 5. ND and NE refer to the number of terminals each D and E side respectively.

- bimension b applies to the metallized terminal and is measured between 0.15mm and 0.3mm from the terminal tip. If the terminal has a radius on the other end of it, dimension b should not be measured in that radius area.

- A Coplanarity applies to the terminals and all other bottom surface metallization.

|                  | Dime | ension Tab | le   |      |

|------------------|------|------------|------|------|

| Symbel Thickness | Min  | Nominal    | Max  | Note |

| A                | 0.80 | 0.90       | 1.00 |      |

| A1               | 0.00 | 0.02       | 0.05 | -    |

| A3               |      | 0.203 Ref. |      |      |

| b                | 0.25 | 0.30       | 0.35 | 6    |

| D                |      | 4.00 BSC   |      |      |

| E                |      | 4.00 BSC   |      | 2    |

| е                |      | 0.65 BSC   |      |      |

| D2               | 2.35 | 2.40       | 2.45 |      |

| E2               | 2.35 | 2.40       | 2.45 |      |

| К                | 0.20 |            |      | 2    |

| L                | 0.45 | 0.55       | 0.65 |      |

| aaa              |      | 2          |      |      |

| bbb              |      | 0.10       |      |      |

| ccc              |      | 0.10       |      |      |

| ddd              |      | 0.05       |      | ·    |

| eee              | 0.08 |            |      |      |

| N                | 16   |            |      | 3    |

| ND               | 4    |            |      | 5    |

| NE               | 4    |            |      | 5    |

| NOTES            | 1,2  |            |      |      |

Figure 32. Package Outline Dimension

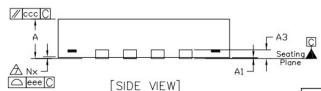

### 5 MHz-9000 MHz

Tape & Reel

Figure 33. Tape & Reel Information

8mm

1000EA

**Device Cavity Pitch**

Device Per Reel

BeRex ●website: <u>www.berex.com</u> ●email: <u>sales@berex.com</u> 13

### 5 MHz-9000 MHz

### **Package Marking**

| Marking information: |                  |  |  |

|----------------------|------------------|--|--|

| BSW6620              | Device Name      |  |  |

| YY                   | Year             |  |  |

| ww                   | Work Week        |  |  |

| XX                   | Wafer Lot Number |  |  |

Figure 34. Package Marking

### Lead plating finish

#### 100% Tin Matte finish

(All BeRex products undergoes a 1 hour, 150 degree C, Anneal bake to eliminate thin whisker growth concerns.)

### MSL / ESD Rating

| ESD information1: |                            |  |

|-------------------|----------------------------|--|

| Rating            | Class 2 (±2000V)           |  |

| Test              | Human Body Model (HBM)     |  |

| Standard          | JEDEC Standard JS-001-2017 |  |

| MSL information: |                                     |  |  |

|------------------|-------------------------------------|--|--|

| Rating           | Level 1 at +260°C convection reflow |  |  |

| Standard         | JEDEC Standard J-STD-020            |  |  |

| ESD information2 : |                            |  |  |

|--------------------|----------------------------|--|--|

| Rating             | Class C3 (±1000V)          |  |  |

| Test               | Charged Device Model (CDM) |  |  |

| Standard           | JEDEC Standard JS-002-2018 |  |  |

Proper ESD procedures should be followed when handling the device.

### **RoHS Compliance**

This part is compliant with Restrictions on the use of certain Hazardous Substances in Electrical and Electronic Equipment (RoHS) Directive 2011/65/EU as amended by Directive 2015/863/EU.

This product also is compliant with a concentration of the Substances of Very High Concern (SVHC) candidate list which are contained in a quantity of less than 0.1%(w/w) in each components of a product and/or its packaging placed on the European Community market by the BeRex and Suppliers.

#### **NATO CAGE code:**

| 2 N | 9 | 6 | F |

|-----|---|---|---|

|-----|---|---|---|

BeRex •website: www.berex.com •email: sales@berex.com